高級模擬集成電路設計的挑戰、機遇與前沿技術

模擬集成電路設計作為電子工業的基石,盡管在數字電路的浪潮下顯得相對低調,但其在信號處理、電源管理、傳感器接口以及無線通信等關鍵領域的重要性從未減弱。隨著系統對性能、功耗和集成度的要求不斷提升,高級模擬集成電路設計正面臨著前所未有的挑戰與機遇。

一、 核心挑戰:精度的極限與工藝的制約

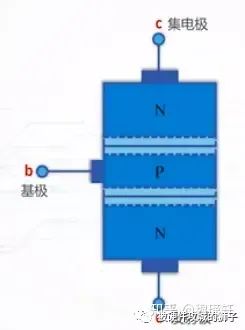

與數字電路追求速度和面積不同,模擬電路設計的核心在于對電壓、電流、頻率等模擬量的精確控制和處理。在先進工藝節點下,晶體管尺寸的持續微縮帶來了諸多不利影響:

- 電源電壓下降與信噪比惡化:更低的電源電壓直接壓縮了信號擺幅,使得電路更容易受到噪聲干擾,設計高精度放大器、比較器和數據轉換器的難度急劇增加。

- 器件非理想特性加劇:短溝道效應、遷移率退化、閾值電壓變化以及器件匹配性的下降,使得傳統設計方法不再適用,設計師必須采用更復雜的電路結構和校準技術來補償這些缺陷。

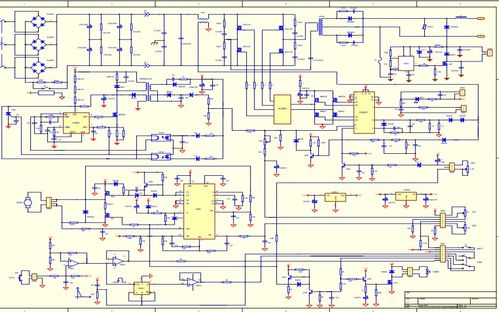

- 寄生效應主導:在納米尺度下,互連線的電阻、電容和電感等寄生參數的影響常常超過有源器件本身,對電路的頻率響應、穩定性和功耗產生決定性影響,版圖設計的重要性被提升到與電路設計同等甚至更高的地位。

二、 設計機遇:系統級集成與智能化輔助

挑戰的另一面是巨大的創新空間和發展機遇:

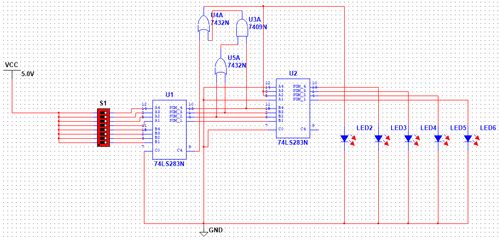

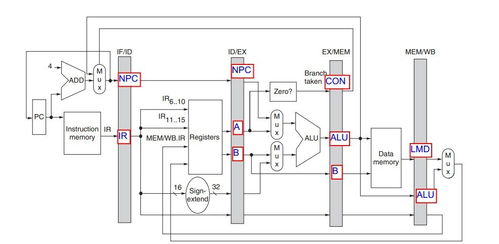

- 混合信號SoC的深度融合:現代芯片大多是復雜的片上系統,模擬前端與數字處理內核的協同設計成為關鍵。這要求模擬設計師不僅精通本領域,還需理解數字系統架構、時鐘分配和電源噪聲隔離等跨域知識。

- 新器件與新材料的應用:FD-SOI、FinFET等新型晶體管結構,以及MEMS傳感器、硅光電子等技術的成熟,為模擬電路開辟了新的應用場景,如超低功耗生物醫療芯片、高速光通信收發器等。

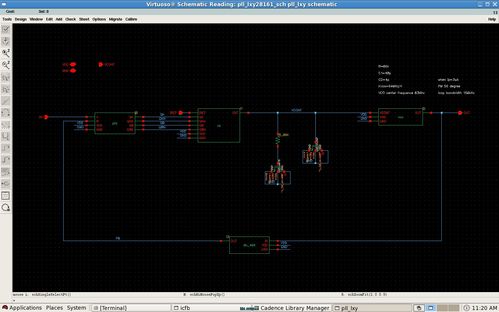

- 設計自動化與AI的賦能:長期以來,模擬設計高度依賴工程師的經驗。如今,機器學習算法正被用于優化電路參數、預測性能、輔助版圖布局布線,甚至進行拓撲結構探索,有望大幅提升設計效率和首次流片成功率。

三、 前沿技術與發展趨勢

- 高性能數據轉換器:面向5G/6G通信和高速數據采集,時間交織、逐次逼近型和連續時間Σ-Δ型ADC正朝著更高速度、更高精度和更低功耗的方向發展,數字后臺校準技術成為標配。

- 面向特定領域的定制化設計:針對人工智能邊緣計算、自動駕駛雷達、量子計算控制等新興領域,模擬電路不再追求通用性,而是與算法深度綁定,進行極致的功耗、速度和精度優化。

- 可靠性與穩健性設計:隨著芯片進入汽車、工業等關鍵任務領域,模擬電路必須在各種工藝角、電壓和溫度變化下保持穩定性能。自適應偏置、片上監控和容錯設計等技術變得越來越重要。

結論

高級模擬集成電路設計正處在一個從經典走向現代的關鍵轉折點。它不再僅僅是“藝術”,而是逐漸演變為一門深度融合了器件物理、系統架構、算法和自動化工具的精密工程學科。未來的模擬設計大師,將是那些能夠駕馭先進工藝、精通跨域知識并善于利用智能工具,以解決復雜系統級問題的工程師。在萬物互聯與智能化的時代,模擬電路作為連接物理世界與數字世界的橋梁,其價值與創新活力必將持續閃耀。

如若轉載,請注明出處:http://m.braccialini.com.cn/product/57.html

更新時間:2026-04-14 10:50:25