集成電路設(shè)計在電路板開發(fā)中的關(guān)鍵作用

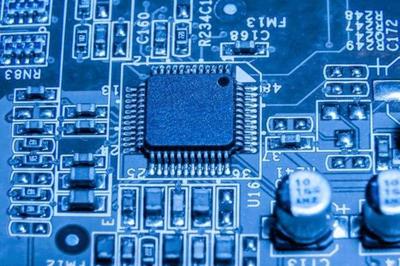

集成電路設(shè)計是現(xiàn)代電子設(shè)備電路板開發(fā)的核心環(huán)節(jié),它不僅決定了電路板的性能和功能,還直接影響產(chǎn)品的尺寸、功耗和成本。集成電路設(shè)計的過程通常包括系統(tǒng)規(guī)劃、邏輯設(shè)計、電路設(shè)計、物理設(shè)計以及測試驗證等階段。

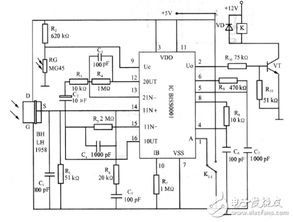

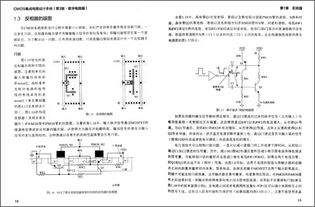

在系統(tǒng)規(guī)劃階段,設(shè)計師根據(jù)電路板的功能需求定義芯片的架構(gòu)和模塊劃分。邏輯設(shè)計階段則利用硬件描述語言(如VHDL或Verilog)構(gòu)建芯片的邏輯功能。隨后,電路設(shè)計將邏輯轉(zhuǎn)換為具體的晶體管級電路,考慮時序、功耗和信號完整性等因素。物理設(shè)計階段負(fù)責(zé)電路布局與布線,確保芯片在制造過程中的可行性和性能優(yōu)化。

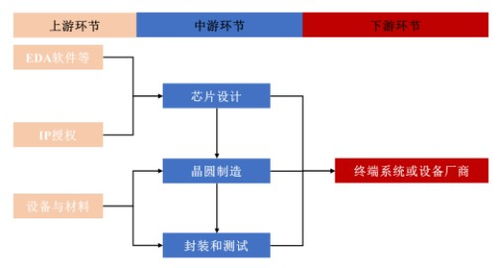

隨著技術(shù)的發(fā)展,集成電路設(shè)計已從傳統(tǒng)的手工繪制發(fā)展到高度自動化的EDA(電子設(shè)計自動化)工具輔助,大大提高了設(shè)計效率和精度。現(xiàn)代集成電路設(shè)計還面臨低功耗、高集成度和可制造性等挑戰(zhàn),推動著新材料和新工藝的不斷涌現(xiàn)。

集成電路設(shè)計是電路板成功的關(guān)鍵,它融合了電子工程、計算機(jī)科學(xué)和材料學(xué)等多學(xué)科知識,持續(xù)推動著電子產(chǎn)品的創(chuàng)新與進(jìn)步。

如若轉(zhuǎn)載,請注明出處:http://m.braccialini.com.cn/product/23.html

更新時間:2026-04-28 16:14:15